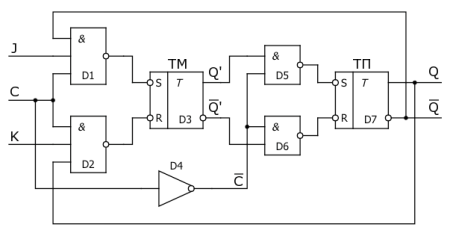

Рис. 2.50.a. Преобразование синхронного RS-триггера в JK-триггер;

JK-триггеры подразделяются на универсальные и комбинированные. Универсальный JK-триггер имеет два информационных входа J и K. По входу J триггер устанавливается в состояние Q=1, /Q=0, а по входу K-в состояние Q=0, /Q=1.

JK-триггер отличается от RS-триггера прежде всего тем что в нем устранена неопределенность, которая возникает в RS-триггере при определенной комбинации входных сигналов.

Универсальность JK-триггера состоит в том, что он может выполнять функции RS-, Т- и D-триггеров.

Комбинированный JK-триггер отличается от универсального наличием дополнительных асинхронных входов S и R для предварительной установки триггера в определенное состояние (логической 1 или 0).

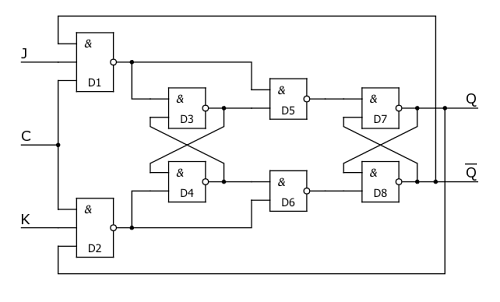

Простейший JK-триггер можно получить из синхронного RS-триггера с динамическим управлением, если ввести дополнительные обратные связи с выходов триггера на входы, которые позволяют устранить неопределенность в таблице состояний (рис. 2.50.а).

Если на входы J и К подать уровень логической единицы, то получим T-триггер, который переключается каждым входным импульсом (рис. 2.50, б).

На рис. 2.50.в приведено условное обозначение JK-триггера и таблица состояний. При входных сигналах J=К=0 состояние триггера не изменяется, так как напряжение низкого уровня на одном входе элемента И-НЕ отменяет пpохождение сигналов от других его входов и удерживает выходной сигнал в текущем логическом состоянии.

| Установлено | Записано | ||

|---|---|---|---|

| J | K | Qn+1 | /Qn+1 |

| H | H | Без изменений Qn /Qn | |

| Н | В | Н=0 | В=1 |

| В | Н | В=1 | Н=0 |

| В | В | Переброс /Qn Qn | |

Если на входы J и К подать взаимно противоположные уровни, то при подаче перепада напряжения на вход С выходы JK-триггера устанавливаются в такие же состояния. При подаче на входы J и К одновременно напряжений высокого уровня триггер переключается в состояние, противоположное предыдущему, если на вход синхронизации С подать перепад напряжения.

Управление полным тактовым импульсом, подаваемым на вход С, применяется для двухступенчатых триггеров (рис. 2.50.г).

Такой триггер тоже имеет обратные связи с выходов на входы, исключающие неопределенное состояние триггера.

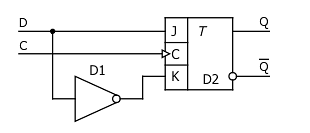

Из JK-триггера можно получить D-триггер, если вход К соединить со входом J через дополнительный инвертор (рис. 2.50,д).

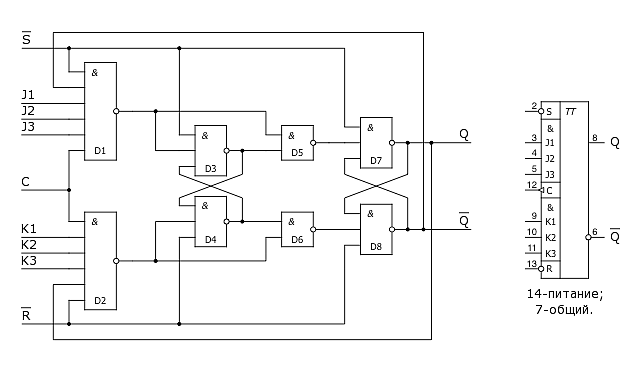

Микросхема TB1 (рис. 2.51) представляет собой универсальный двухступенчатый JK-триггер.

Триггер имеет инверсные асинхронные входы установки /S и сброса /R, т. е. с активным низким уровнем. Если на эти входы подать противоположные уровни (низкий - 0 и высокий - 1), то входы J, K и С не действуют и состояния выходов Q и /Q триггера определяются сигналами на входах /S и /R, таблица состояний (табл. 2.27).

| Режим работы | Входы | Выходы | |||||

|---|---|---|---|---|---|---|---|

| /S | /R | J | K | C | Qn+1 | /Qn+1 | |

| Асинхронная установка | 0 | 1 | Х | Х | Х | 1 | 0 |

| Асинхронный сброс | 1 | 0 | Х | Х | Х | 0 | 1 |

| Неопределенность | 0 | 0 | Х | Х | Х | X | X |

| Загрузка "1" (установка) | 1 | 1 | 1 | 0 | _/\_ | 1 | 0 |

| Загрузка "0" (сброс) | 1 | 1 | 0 | 1 | _/\_ | 0 | 1 |

| Переключение | 1 | 1 | 1 | 1 | _/\_ | /Qn | Qn |

| Хранение (нет изменений) | 1 | 1 | 0 | 0 | _/\_ | Qn | /Qn |

Когда на входы /S и /R поданы напряжения высокого уровня, в триггер можно загружать информацию от входов J и K или хранить ее (см. таблицу состояний). Каждый из входов J и K снабжен логическим элементом 3И, т.е. микросхема ТВ1 имеет три входа J и три входа K. Вход синхронизации C инверсный динамический. Состояния двухступенчатого триггера переключаются фронтом и спадом положительного импульса, подаваемого на вход синхронизации C. Информация со входов J и K загружается в триггер первой ступени (элементы DD1.3 и DD1.4), когда напряжение входа C изменяется от низкого уровня к высокому (по фронту) и переносится в триггер второй ступени по отрицательному перепаду импульса синхронизации (по спаду). Сигналы на входах J и K не должны изменяться, если на входе /C присутствует напряжение высокого уровня. Состояния выходов Q и /Q будут неопределенные, если на входы /S и /R одновременно подать напряжение низкого уровня, т. е. комбинация сигналов /S=/R=0 является запрещенной.

Микросхемы ТВ6 и ТВ9, ТВ10 и TB11 содержат по два JK-триггера с общим выводом питания (рис. 2.52).

Вход синхронизации С у всех триггеров инверсный динамический, поэтому данные от входов J и К переносятся на выходы Q и /Q по отрицательному перепаду импульса С. Когда импульс на входе С переходит от высокого уровня к низкому, сигналы на входах J и К не должны изменяться. Информацию от входов J и К следует загружать в триггер, когда на входе С присутствует напряжение высокого уровня.

У триггеров микросхемы ТВ6 нет входа предварительной установки /S, поэтому в таблице состояний (комбинированного JK-триггера) необходимо исключить первую строку (асинхронную установку 1). Если на вход /R будет подано напряжение низкого уровня, то входы J, К и С не действуют.

У триггеров микросхемы ТВ10 нет входа предварительного сброса /R, поэтому в таблице состояний комбинированного JK-триггера необходимо исключить вторую строку (асинхронный сброс 0).

Для микросхем ТВ6 и ТВ10 в таблице состояний не имеет смысла и третья строка, т. к, они имеют только по одному асинхронному входу (либо /S, либо /R). Триггеры микросхемы ТВ11 в отличие от триггеров микросхемы ТВ9 имеют две общие цепи управления: вход синхронизации /С и асинхронный вход сброса /R (рис. 2.53).

Микросхемы ТВ14 и ТВ15 содержат по два комбинированных JK-триггера, которые запускаются положительным перепадом импульса синхронизации, т. е. вход С прямой динамический. Отличительной особенностью триггеров данных микросхем является то, что второй информационный вход /К - инверсный, поэтому очень легко такие JK-триггеры превращать в D-триггеры (рис. 2.54).

Состояние таких триггеров приведено в табл. 2.28.

| Режим работы | Входы | Выходы | |||||

|---|---|---|---|---|---|---|---|

| /S | /R | J | /K | C | Qn+1 | /Qn+1 | |

| Асинхронная установка | 0 | 1 | X | X | X | 1 | 0 |

| Асинхронный сброс | 1 | 0 | X | X | X | 0 | 1 |

| Неопределенность | 0 | 0 | X | X | X | 1 | 1 |

| Загрузка "1" (установка) | 1 | 1 | 1 | 0 | _/\_ | 1 | 0 |

| Загрузка "0" (сброс) | 1 | 1 | 0 | 1 | _/\_ | 0 | 1 |

| Переключение | 1 | 1 | 1 | 0 | _/\_ | /Qn=1 | Qn=0 |

| Хранение (нет изменений) | 1 | 1 | 0 | 1 | _/\_ | 1 | 0 |

Основные параметры триггеров ТТЛ приведены в табл.2.20.